#### Abstract

This application note describes the implementation of a hybrid TV receiver capable of handling both analogue and digital transmissions with one tuner. During the transition phase from analogue towards full digital transmissions, these hybrid TV receivers are needed in the market.

The aimed market segment for the presented concept is called LMR-DTV. A "low" range digital source decoding part (designed as an "add-on") is economicly combined (via a new designed interface) with a mid range analogue 110<sup>o</sup>, 16:9 TV receiver.

The receiver was build as a demonstrator and is part of the LMR-DTV system study of PS-SLE.

The analogue part is based on the TDA8885 version of the Philips Semiconductor one chip TV IC family, designed for the European market and thertefore not full RF multi standard. Via the tuner PAL-B/G-I-DK, SECAM-B/G-D/K-L-L1 is implemented. Via external inputs this is extended with NTSC-M, PAL-N,-M.

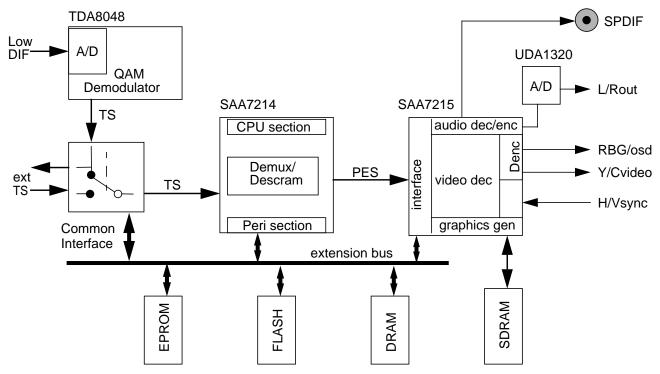

For the digital part, two channel decoding options are worked out: DVB-C and DVB-T. For the COFDM demodulator the VES9600 is used. The MPEG-2 source decoding part is implemented with the SAA7214 and SAA7215 as used for the Philips Semiconductors set-top box reference design STB5660.

With rewritten and adapted embedded software, the possibility for **one** user interface (all OSD/OSG generated by SAA7215) for both analogue and digital frondend modes is shown.

The full working hybrid TV receiver was build and demonstrated to external customers by PS-SLE at the Philips Semiconductor show held in Hotel Berlin during the IFA in august 1999.

Purchase of Philips  $I^2C$  components conveys a license under the Philips  $I^2C$  patent to use the components in the  $I^2C$  system, provided the system conforms to the  $I^2C$  specifications defined by Philips.

#### © Philips Electronics N.V. 2000

All rights are reserved. Reproduction in whole or in part is prohibited without the prior written consent of the copyright owner.

The information presented in this document does not form part of any quotation or contract, is believed to be accurate and reliable and may be changed without notice. No liability will be accepted by the publisher for any consequence of its use. Publication thereof does not convey nor imply any license under patent- or other industrial or intellectual property rights.

Application Note AN99061

# **APPLICATION NOTE**

# Hybrid Analogue/DVB TV Receiver IFA1999 Demonstrator

## AN99061

#### Author(s):

M. de Bakker (SW) R. van den Eijnden (HW) T. Hummelink (HW) J. van Nieuwenburg (HW) P. Noordhoek (HW/SW) E. Wilms (SW) Philips Semiconductors Systems Laboratory Eindhoven, The Netherlands

#### Keywords

LMR-DTV DVB-T DVB-C Hybrid Bocma Painter GreenChip Digital TV

Number of pages: 78 Date: 2000-01-04

#### Summary

This application note describes the implementation of a hybrid TV receiver capable of handling both analogue and digital transmissions.

The analogue part is based on the TDA8885 version of the Philips Semiconductor one chip TV IC family. The receiver is designed for the European market and thertefore not full multi standard. Via the tuner PAL-B/G-I-DK, SECAM-B/G-D/K-L-L1 is implemented. Via external inputs this is extended with NTSC-M, PAL-N,-M.

For the audio part, the Philips multsitandard TV sound processor TDA9875A is used. The speakers are driven by the new TDA8946 sound amplifiers.

For the digital part, two channel decoding options are worked out: DVB-C and DVB-T. For the COFDM demodulator the VES9600 is used. The MPEG-2 source decoding part is implemented with the SAA7214 and SAA7215 as used for the Philips Semiconductors set-top box reference design STB5660.

The reception for both transmissions can be done via one tuner. The Philips CD1516 for analogue and digital cable transmissions and the TD1544 for analogue and digital terrestrial transmissions.

The used video amplifier is a TDA6108 and has a bandwidth of 9Mhz (100Vpp). No alignment at the board is necessary, it is done via IIC-bus.

The 200W power supply is build around the TEA1504 GreenChip SMPS controller. Vertical deflection is made with the new LVDMOS driver family TDA8359.

The deflection supports linear zoom in vertical AND horizontal direction (Philips patent), all geometry control for the Philips RealFlat picture tubes is present. The demo receiver is made with a 32 inch RealFlat tube.

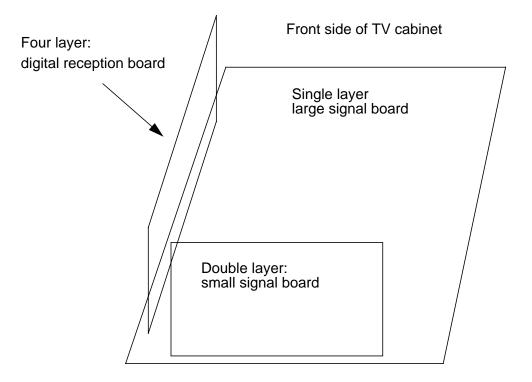

The receiver is made modular and split in three parts:

- 1. A single layer large signal board

- 2. A double layer small signal board

- 3. A four layer digital board

With rewritten and adapted embedded software, the possibility for **one** user interface (all OSD/OSG generated by SAA7215) for both analogue and digital frondend modes is shown. A short software user manual is described and also the known problem list.

This Application Note should be read together with the Application Note AN99062. On an A3 paper size the diagrams, layouts and bill of materials are presented.

The report is not complete yet. In a next version the system overview of the power supply &deflection, has to be added. The EMC part describes now the design aspects. Later on this chapter has to be expanded with the EMC measurements, results and improvement of the total system.

# Application Note AN99061

## **Table of Contents**

| 1. | Introd | uction        |               |       |             |   |   |   | <br> | <br>    | <br>    |     | . 9 |

|----|--------|---------------|---------------|-------|-------------|---|---|---|------|---------|---------|-----|-----|

| 2. | Syster | n Overview    |               |       |             |   |   |   | <br> | <br>    | <br>    |     | 11  |

|    | 2.1    | Design Spec   | cifications.  |       |             |   |   |   | <br> | <br>    | <br>    |     | 11  |

|    | 2.2    | Board Setup   |               |       |             |   |   |   |      |         |         |     |     |

|    | 2.3    | Design Cons   | siderations   |       |             |   |   |   | <br> | <br>    | <br>    |     | 15  |

|    | 2.4    | Analogue &    | Digital Inter | rface |             |   |   |   | <br> | <br>    | <br>    |     | 17  |

|    | 2.5    | Block diagra  | •             |       |             |   |   |   |      |         |         |     |     |

|    |        |               | nalogue &     |       |             |   |   |   |      |         |         |     |     |

|    |        |               | nalogue Re    | -     |             |   |   |   |      |         |         |     |     |

|    |        |               | igital Rece   | •     |             |   |   |   |      |         |         |     |     |

|    |        |               | ower Supp     | •     |             |   |   |   |      |         |         |     |     |

| 3. | Analo  | gue Receptic  | on Part       |       |             |   |   |   | <br> | <br>    | <br>    |     | 23  |

|    | 3.1    | Tuner & IF F  |               |       |             |   |   |   |      |         |         |     |     |

|    | 011    |               | nalogue on    |       |             |   |   |   |      |         |         |     |     |

|    |        |               | nalogue an    |       |             |   |   |   |      |         |         |     |     |

|    |        |               | .1.2.1        | 0     | part DVB-(  |   |   | ' |      |         |         |     |     |

|    |        | -             | .1.2.2        | •     | part DVB-   |   |   |   |      |         |         |     |     |

|    | 3.2    | OneChip TV    |               | •     | •           |   |   |   |      |         |         |     |     |

|    | 0.2    | •             | BOCMA IF p    | •     | ,           |   |   |   |      |         |         |     |     |

|    |        |               | colour deco   |       |             |   |   |   |      |         |         |     |     |

|    |        |               | UV interfac   | •     |             |   |   |   |      |         |         |     |     |

|    |        |               | icture impre  |       |             |   |   |   |      |         |         |     |     |

|    |        |               | .2.4.1        |       | pendent co  |   |   |   |      |         |         |     |     |

|    |        | -             | .2.4.2        |       | ansient imp |   |   |   |      |         |         |     |     |

|    |        | -             | .2.4.3        |       | skin contro |   | • |   |      |         |         |     |     |

|    |        |               | .2.4.4        | •     | hancement   |   |   |   |      |         |         |     |     |

|    |        | -             | .2.4.5        |       | etch        |   |   |   |      |         |         |     |     |

|    |        |               | .2.4.6        |       | etch        |   |   |   |      |         |         |     |     |

|    |        |               | .2.4.7        |       | ch          |   |   |   |      |         |         |     |     |

|    |        | -             | GB outputs    |       |             |   |   |   |      |         |         |     |     |

|    | 3.3    | Comb filter   | •             |       |             |   |   |   |      |         |         |     |     |

|    | 3.4    | Peri & Switc  |               |       |             |   |   |   |      |         |         |     |     |

|    | 011    |               | V Status de   |       |             |   |   |   |      |         |         |     |     |

|    | 3.5    | TV Control F  |               |       |             |   |   |   |      |         |         |     |     |

|    | 0.0    |               | Control lines |       | ` '         |   |   |   |      |         |         |     |     |

|    |        |               | Control lines | -     | •           | • |   |   |      |         |         |     |     |

|    |        |               | ocal Keybo    |       |             |   |   |   |      |         |         |     |     |

|    |        |               | VBSText.      |       |             |   |   |   |      |         |         |     |     |

|    |        |               | SD RGB o      |       |             |   |   |   |      |         |         |     |     |

|    |        |               | Synchroniza   | •     |             |   |   |   |      |         |         |     |     |

|    |        |               | leset and si  |       |             |   |   |   |      |         |         |     |     |

|    | 3.6    | Digital TV Se |               |       |             |   |   |   |      |         |         |     |     |

|    | 3.7    | Sound Optio   |               |       | • •         |   |   |   |      |         |         |     |     |

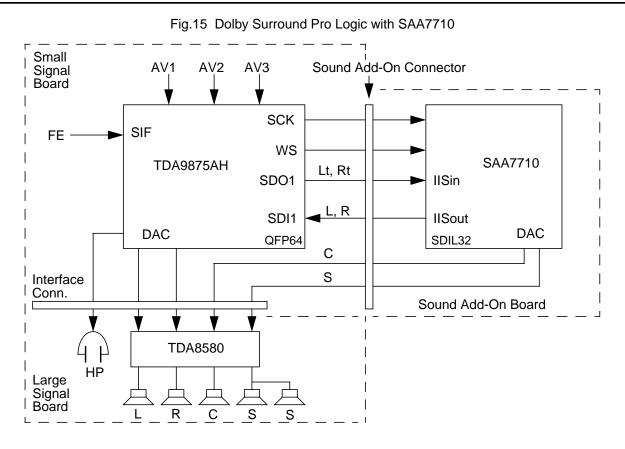

|    | 0.1    |               | olby Surro    |       |             |   |   |   |      |         |         |     |     |

|    |        | J D           | Siby Sund     |       | 9.0         |   |   |   | <br> | <br>• • | <br>• • | • • | 55  |

# Application Note AN99061

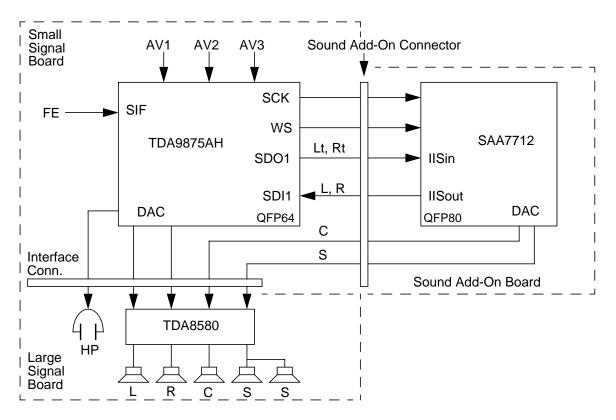

|    |         | 3.7.2       | Virtual Dolby  | Surround Pro Logic with SAA7712           |    |

|----|---------|-------------|----------------|-------------------------------------------|----|

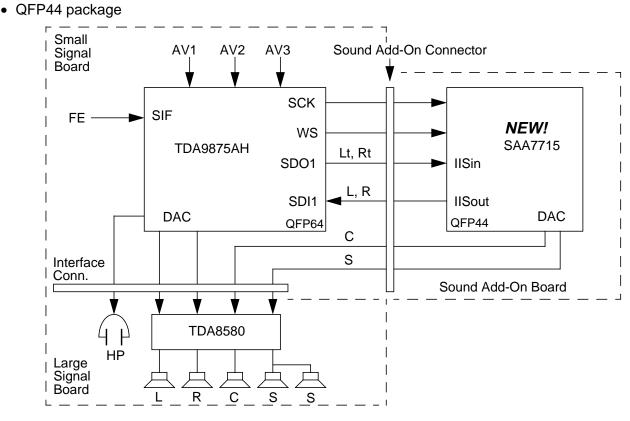

|    |         | 3.7.3       | (Virtual) Dolt | y Surround Pro Logic with new SAA7715.    | 43 |

|    |         | 3.7.4       |                | g with SAA2505 and post-processing with S |    |

| 4. | Digital | Percention  | Dort           |                                           | 47 |

| 4. | •       | •           |                |                                           |    |

|    | 4.1     |             |                |                                           |    |

|    | 4.2     | -           |                | art                                       |    |

|    | 4.3     |             | •              |                                           |    |

|    |         | 4.3.1       | -              |                                           | -  |

|    |         | 4.3.2       |                |                                           |    |

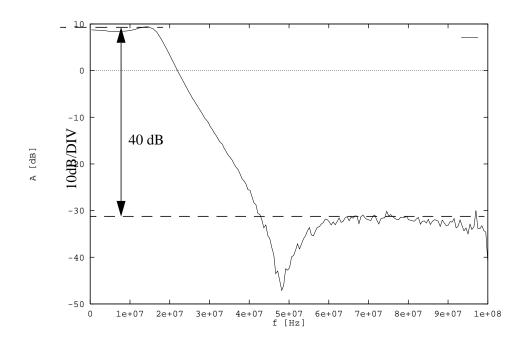

|    |         |             | 4.3.2.1        | Low-IF ADC pre-filter                     |    |

|    |         |             | 4.3.2.2        | Input circuitry                           | 50 |

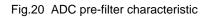

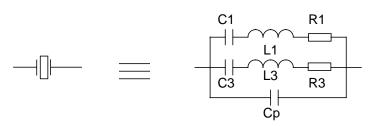

|    |         |             | 4.3.2.3        | Crystal oscillator                        | 50 |

|    |         |             | 4.3.2.4        | Preset                                    |    |

|    |         |             | 4.3.2.5        | VAGC                                      |    |

|    |         |             | 4.3.2.6        | itop                                      |    |

|    |         |             | 4.3.2.7        | Transport stream                          |    |

|    |         | 4.3.3       | DVB-T          |                                           |    |

|    | 4.4     | MPEG-2 S    |                | 9r                                        |    |

|    |         | 4.4.1       |                |                                           |    |

|    |         | 4.4.2       |                |                                           |    |

|    |         | 4.4.3       |                |                                           |    |

|    |         | 4.4.4       |                |                                           |    |

|    |         | 4.4.4       | 4.4.4.1        | RESETn                                    |    |

|    |         |             | 4.4.4.2        | Oscillator/PWM[0]                         |    |

|    | 4.5     |             |                |                                           |    |

|    | 4.0     | 4.5.1       |                |                                           |    |

|    |         | -           |                |                                           |    |

|    |         | 4.5.2       |                | ntry stream                               |    |

|    |         | 4.5.3       |                | facing                                    |    |

|    |         |             | 4.5.3.1        |                                           |    |

|    |         | 4.5.4       | •              | SAA7215                                   |    |

|    |         |             | 4.5.4.1        | Analogue Video                            |    |

|    |         |             | 4.5.4.2        | Sound                                     |    |

|    | 4.6     |             | 0              |                                           |    |

|    | 4.7     | Board Inte  | erfaces & Con  | ectors                                    |    |

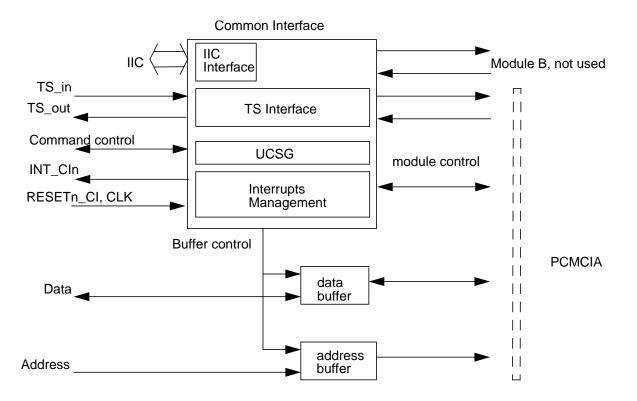

|    |         | 4.7.1       | Common Inte    | rface                                     |    |

|    |         | 4.7.2       | RS232          |                                           |    |

|    |         | 4.7.3       | SPDIF          |                                           |    |

|    | 4.8     | Debug Ha    | rdware Suppo   | rt                                        |    |

|    |         | 4.8.1       | Debug conne    | ctors                                     |    |

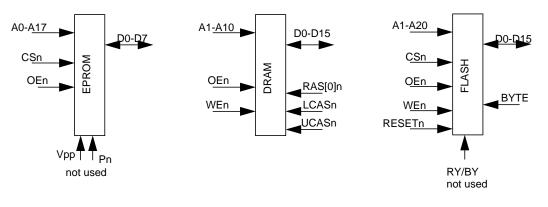

|    |         | 4.8.2       | Boot from fla  | h1 or ROM                                 |    |

|    |         | 4.8.3       | Download to    | ílash                                     |    |

|    |         | 4.8.4       |                |                                           |    |

|    |         |             |                |                                           |    |

| 5. |         |             |                |                                           |    |

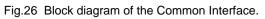

|    | 5.1     | •           |                |                                           |    |

|    | 5.2     |             |                |                                           |    |

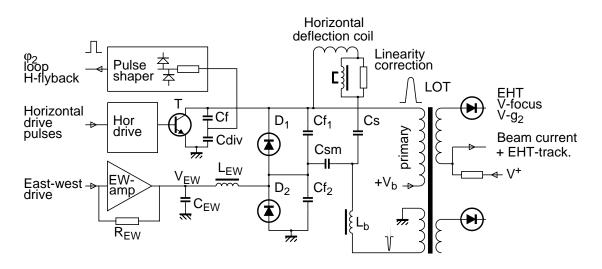

|    | 5.3     | Vertical De | eflection      |                                           | 62 |

# Application Note AN99061

| 6. | Softwa | are         |                |          |       |     |     |     |     |     |     |   |     |     |     |   |     |   |     |   |     |   |     |   | 65 |

|----|--------|-------------|----------------|----------|-------|-----|-----|-----|-----|-----|-----|---|-----|-----|-----|---|-----|---|-----|---|-----|---|-----|---|----|

|    | 6.1    | Install Mer | nu             |          |       |     |     |     |     |     |     |   |     |     |     |   |     |   |     |   |     |   |     |   | 65 |

|    |        | 6.1.1       | Prog. Nr       |          |       |     |     |     |     |     |     |   |     |     |     |   |     |   |     |   |     |   |     |   | 65 |

|    |        | 6.1.2       | System         |          |       |     |     |     |     |     |     |   |     |     |     |   |     |   |     |   |     |   |     |   | 65 |

|    |        | 6.1.3       | Frequency.     |          |       |     |     |     |     |     |     |   |     |     |     |   |     |   |     |   |     |   |     |   | 66 |

|    |        | 6.1.4       | AFC            |          |       |     |     |     |     |     |     |   |     |     |     |   |     |   |     |   |     |   |     |   | 66 |

|    |        | 6.1.5       | Fine Tune .    |          |       |     |     |     |     |     |     |   |     |     |     |   |     |   |     |   |     |   |     |   | 66 |

|    |        | 6.1.6       | Dig Chan .     |          |       |     |     |     |     |     |     |   |     |     |     |   |     |   |     |   |     |   |     |   | 66 |

|    |        | 6.1.7       | PCR PID .      |          |       |     |     |     |     |     |     |   |     |     |     |   |     |   |     |   |     |   |     |   | 66 |

|    |        | 6.1.8       | VID PID        |          |       |     |     |     |     |     |     |   |     |     |     |   |     |   |     |   |     |   |     |   | 66 |

|    |        | 6.1.9       | AUD PID .      |          |       |     |     |     |     |     |     |   |     |     |     |   |     |   |     |   |     |   |     |   | 66 |

|    |        | 6.1.10      | Name           |          |       |     |     |     |     |     |     |   |     |     |     |   |     |   |     |   |     |   |     |   | 67 |

|    |        | 6.1.11      | Store          |          |       |     |     |     |     |     |     |   |     |     |     |   |     |   |     |   |     |   |     |   | 67 |

|    |        | 6.1.12      | Autostore .    |          |       |     |     |     |     |     |     |   |     |     |     |   |     |   |     |   |     |   |     |   | 67 |

|    | 6.2    | Analogue    | keys           |          |       |     |     |     |     |     |     |   |     |     |     |   |     |   |     |   |     |   |     |   | 67 |

|    | 6.3    | Digital der | no mode keys   | S        |       |     |     |     |     |     |     |   |     |     |     | • |     |   |     |   |     |   |     |   | 67 |

|    | 6.4    | Digital Me  | nu's           |          |       |     |     |     |     |     |     |   |     |     |     | • |     |   |     | • |     |   |     |   | 68 |

|    |        | 6.4.1       | General Mer    | nu navig | ation |     |     |     |     |     |     |   |     |     |     | • |     |   |     |   |     |   |     |   | 68 |

|    |        | 6.4.2       | Main menu      |          |       |     |     |     |     |     |     |   |     |     |     | • |     | • |     | • |     |   |     |   | 68 |

|    |        | 6.4.3       | Installation N | lenu .   |       |     |     |     |     |     |     |   |     |     |     | • |     | • |     | • |     |   |     |   | 68 |

|    |        | 6.4.4       | Feature Men    |          |       |     |     |     |     |     |     |   |     |     |     |   |     |   |     |   |     |   |     |   |    |

|    |        |             | 6.4.4.1        | Graphi   | CS .  |     |     |     |     |     |     |   |     |     | •   | • |     | • |     | • |     |   |     |   | 69 |

|    |        |             | 6.4.4.2        | Scaling  | ]     |     |     |     |     |     |     |   |     |     | •   | • |     | • |     | • |     |   |     |   | 70 |

|    |        |             | 6.4.4.3        | Video    |       |     |     |     |     |     |     |   |     |     | •   | • |     | • |     | • |     |   |     |   | 70 |

|    | 6.5    | Known pro   | oblems         |          |       |     |     |     |     |     |     | • |     |     | • • | • |     | • |     | • |     | • |     |   | 70 |

| 7. | EMC.   |             |                |          |       |     |     |     |     |     |     |   |     |     |     |   |     |   |     |   |     |   |     |   | 73 |

| •• | 7.1    |             | spects         |          |       |     |     |     |     |     |     |   |     |     |     |   |     |   |     |   |     |   |     |   |    |

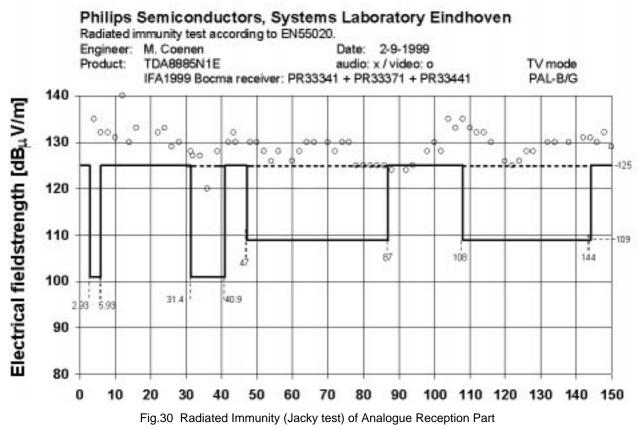

|    | 7.2    |             | Reception pa   |          |       |     |     |     |     |     |     |   |     |     |     |   |     |   |     |   |     |   |     |   |    |

|    | 7.3    | •           | ception Part   |          |       |     |     |     |     |     |     |   |     |     |     |   |     |   |     |   |     |   |     |   |    |

| _  |        | -           |                |          |       |     |     |     |     |     |     |   |     |     |     |   |     |   |     |   |     |   |     |   |    |

| 8. | Abbrev | viations .  |                |          |       | • • | ••• | • • | ••• | • • | • • | · | • • | • • | • • | • | ••• | • | • • | • | • • | · | • • | · | 77 |

| 9. | Refere | nces        |                |          |       |     |     |     |     |     |     |   |     |     |     |   |     |   |     | • |     |   |     |   | 79 |

#### 1. Introduction

This application note describes the implementation of a hybrid TV receiver capable of handling both analogue and digital transmissions. During the transition phase from analogue towards full digital transmissions, these hybrid TV receivers are needed in the market.

In order to enter the high volume market, the introduction price for these hybrid TV receivers must be kept as low as possible. This market segment is idented and named LMR-DTV (Low-end digital, Mid-Range analogue, Digital TeleVision). Several LMR-DTV concepts are made. In this report two implementation are described:

SLE3500 Multistandard Analogue reception combined with DVB-T

SLE3510 Multistandard Analogue reception combined with DVB-C

The work is done as part of a system study. One goal was to present a working model at the Philips Semiconductors show held in Hotel Berlin during IFA'99. Although the DVB-T hybrid is the most important design, within the available time frame the DVB-C hybrid was seen as the most successful candidate to show at IFA. During the project the VES9600 COFDM demodulator became available and the DVB-T combination was also made but with a separate VES9600 board. There was no redesign made with the VES9600 at the place of the DVB-C QAM demodulator. During the IFA the SLE3500 was presented with a via the Common Interface connector connected external VES9600 COFDM demodulator board.

This report must be read together with report AN99062 which contains the diagrams, layouts and bill of materials on an A3 paper size.

On these diagrams the SLE3510 concept is presented. The used DVB\_C QAM demodulator is the outdated TDA8048 device, it will be replaced by VES1820.

The idea of the presented LMR-DTV receiver concept is that one can make a 50Hz Mid-End TV receiver chassis and design it in such way that **without a redesign** one can add a digital reception part to it. In this way it is not necessary to make a dedicated hybrid receiver design.

For this reason the whole receiver is divided into three boards:

- 1. Single layer large signal part.

- 2. Double layer small signal part.

3. Four layer digital reception part which is the optional add-on to make it a hybrid receiver.

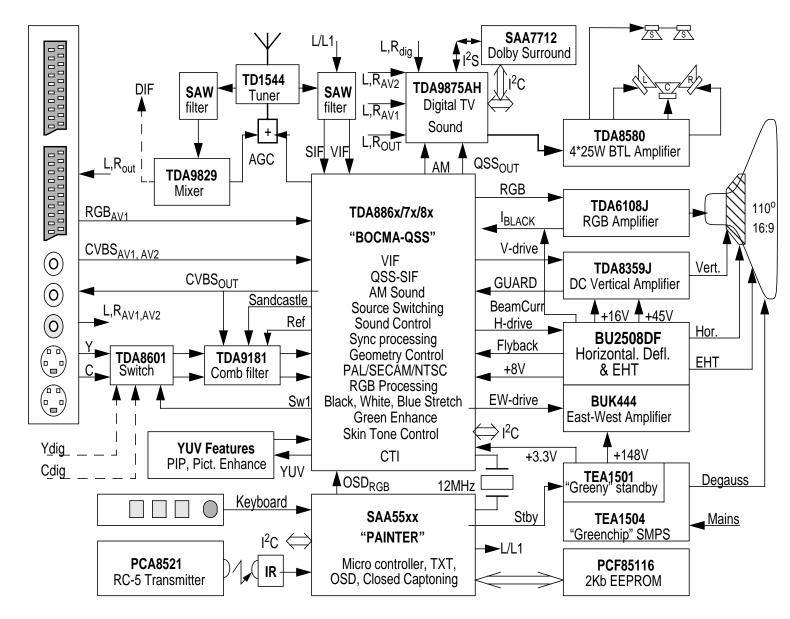

The small signal analogue reception part is based on the TDA8885H version of the one chip TV IC family with development name BOCMA. It also contains the SAA55xx or 56xx micro controller (Painter) and a digital multistandard TV sound device (TDA9875AH) is used.

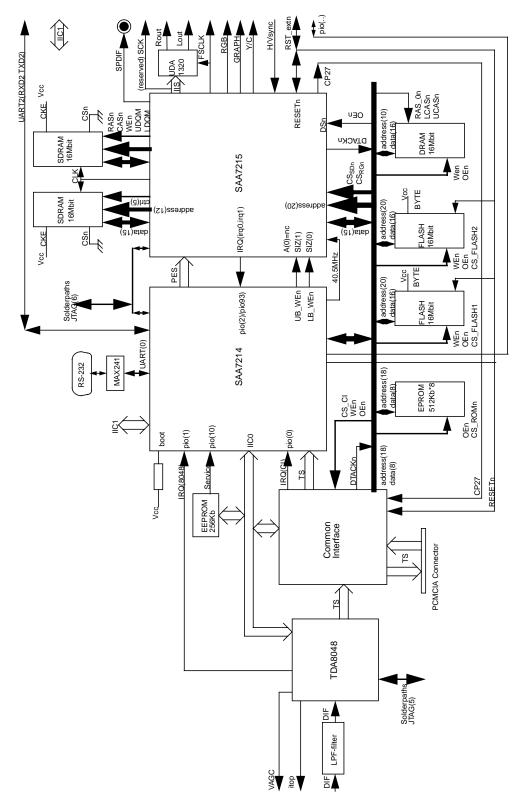

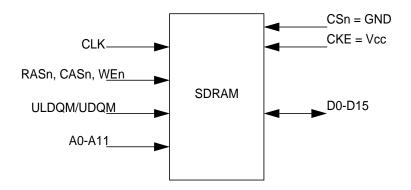

The digital reception part is based on the SAA7214 (MIPS) and SAA7215 (DIVA) MPEG2 source decoding family. To minimise our software effort in the design phase, the outdated SAA7214 is used. In industrial designs it should be replaced by the SAA7219.

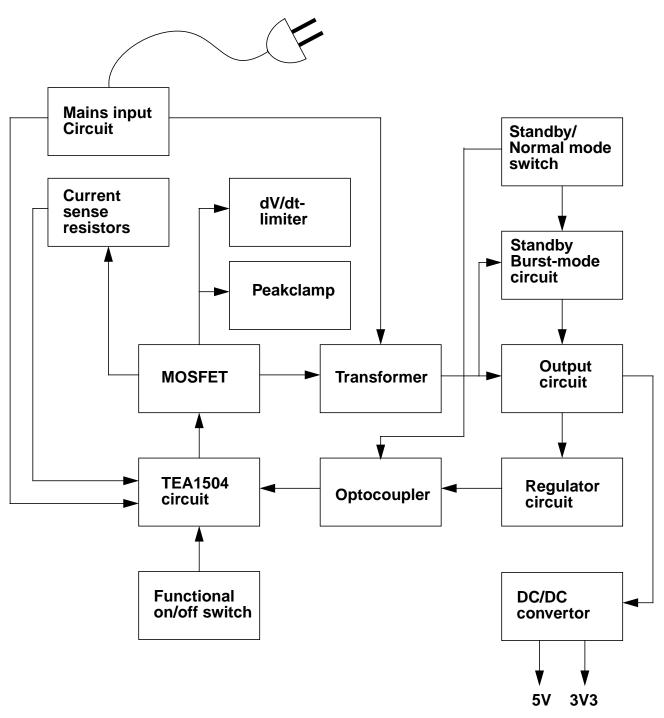

The power supply is based on the new Green Chip SMPS control IC family TEA1504 and TEA1501 (Greeny). Vertical deflection is done with the new TDA8357 vertical driver. Audio amplifying is done by the new TDA894x family (TDA8946). The picture tube is driven with a TDA6108 video amplifier.

With rewritten and adapted embedded software, the possibility for **one** user interface (all OSD/OSG generated by SAA7215) for both analogue and digital frondend modes is implemented. Not **all** analogue OSD control menus are converted to SAA7215. For this demonstrator only the channel number and the volume bar are made equal for both analogue and digital fronden modes.

#### 2. System Overview

This chapter describes the different building blocks of the hybrid TV receiver.

#### 2.1 Design Specifications

The demonstration receiver is designed for the European market. It has the following characteristics:

- Quasi-Split Sound with single reference IF system

- Off-air reception for: SECAM-BG-DK-L-L1, PAL-BG-I-DK video standards

5.5 and 6.5MHz FM mono sound standards, AM France mono, B/G-2CS, NICAM-I and BG stereo standards

NOT: BTSC and Japanese FM to FM stereo

- NTSC-M and PAL-M-N playback via external inputs

- AV1: One full SCART with CVBS in & out, Audio left/right in & out, RGB in (or Y/C in AV1S)

- AV2: Second SCART with CVBS in & out, Audio left/right in & out

- AV2S: S-VHS Y/C Hosiden input (Y in parallel to AV2 CVBS)

- AV3 on front: in this demonstrator only available WITHOUT digital reception part, CVBS in, Audio Left/Right in

- AV3S on front: only available WITHOUT digital reception part, Y/C in (Y in parallel with AV3 CVBS in)

- Stereo headphone 3.5mm output jack connector on front

- Optional Dolby Surround Pro Logic decoding with extra small board

- YUV connector for optional extra picture improvements or a simple PIP application

- Deflection circuitry also prepared for Philips 50Hz real flat picture tube

- Deflection with linear vertical and horizontal zoom capabilities according to SLE patent

- 200W SMPS part, approx. 90W reserved for audio power

- Hybrid Analogue-Digital TV

- Optional Dolby Pro-logic decoding

- MPEG-2 Audio & Video

- PCMCIA Interface Slot

When the digital reception part is added the AV3/AV3S input is sacrificed and used for the video and audio output of the MPEG decoder. Now the next properties are added:

- DVB-C demodulation up to 256-QAM or DVB-T demodulation for COFDM-2k/8k (ETSI 300 744)

- MPEG2 source decoding

- Digital ENCoder (DENC) and ADC to convert back to PAL-CVBS-Y/C, RGB and Left/Right audio

- Digital audio SPDIF output

- RS232

# Application Note AN99061

#### 2.2 Board Setup

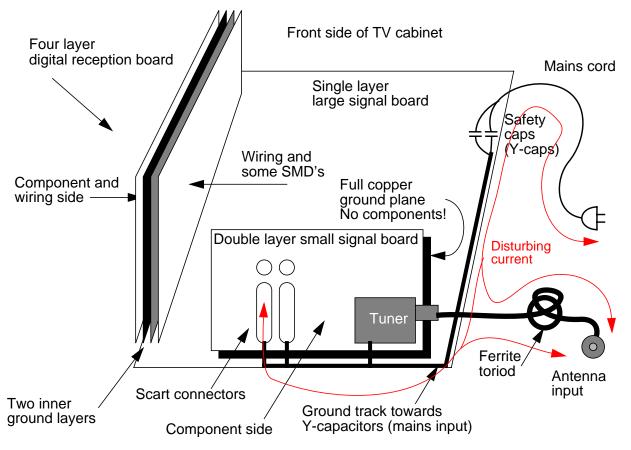

The choice of this concept is to split the TV functions in three parts. The board set up is given below.

Rear side of TV cabinet

#### Fig.1 Board setup

The digital reception board is placed on the edge of the large signal board. Now when only the analogue TV receiver has to be produced, the large signal board needs no redesign. The only difference is that the connector row is not mounted, the large signal board will be smaller and the signal leads to the digital reception board are not routed. The rest remains the same. This is shown in the "Analogue and Digital Interface" paragraph. In this figure the red coloured (or light grey) parts are only needed for the digital add-on. The signal sequence in the connectors are chosen in such way that when the digital add-on is used the other connectors on the small signal board are not needed anymore. The signal sequence in the interface is also optimized for minimum signal crossings. This was needed specially for the small signal board which is in fact a single layer design due to the full copper bottom layer. The remaining crossings are made with isolated wire jumpers which can be replaced by SFR16 0 $\Omega$  jumpers for factory production.

To make our engineering phase more flexible, the large signal part is splitted in two boards. Via the large and small signal interface board PR33441, we can use different power supply and deflection concepts. PR33441 is designed in such way that you can combine the layout of PR33441 and PR33341 to one board.

- 1. Large signal: the combination of PR33441 and PR33341

- 2. Small signal: PR33371

- 3. Digital part: PR33321

## Application Note AN99061

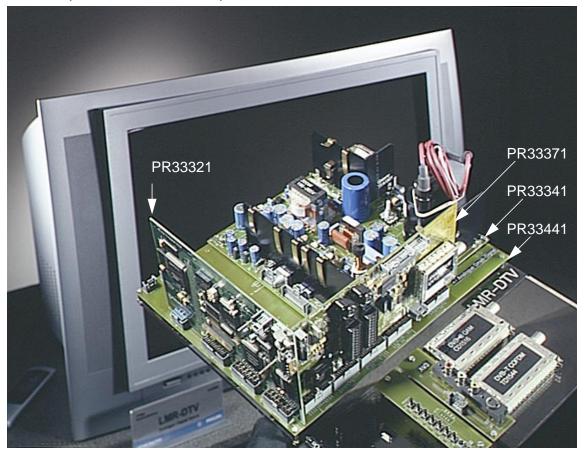

The board setup is shown on the next photo:

Fig.2 Total hardware fotograph

The demo receiver consist of four boards:

- 1. PR33441: Interface Board Large and Small Signal

- 2. PR33341: Large Signal Board (Switch Mode Power Supply & Deflection)

- 3. PR33371: Analogue Reception & Processing Board

- 4. PR33321: Digital Reception & Processing Board

# Application Note AN99061

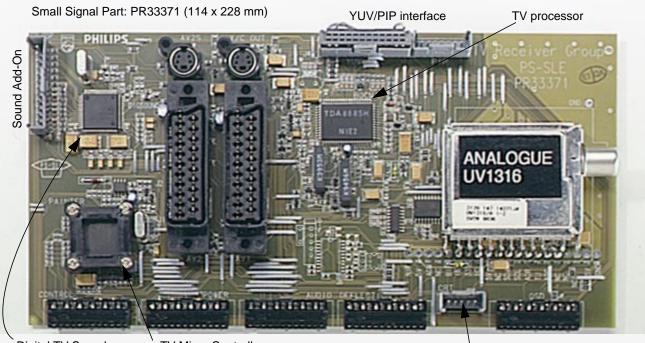

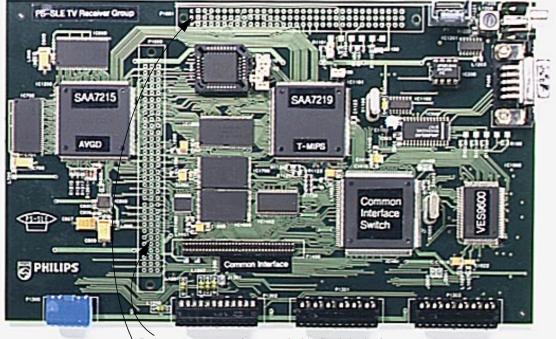

Fig.3 .Small Signal Part & Digital Reception Part photographs

Digital TV Sound

TV Micro Controller

<sup>\</sup> RGB out to CRT panel

Digital Reception Part: PR33321 (125 x 206 mm)

NOTE: on the foto the VES9600 is not the actual device. The new VES9600/R will almost be the same package as on the photo.

Debug connectors (not needed in final design)

# Application Note AN99061

Fig.4 Large Signal Board: combination of PR33441 and PR33341 (total is 250 x 321 mm)

#### 2.3 Design Considerations

The system is split in three parts. Large signal, small signal and optional digital reception part. Now several combinations can be designed without a redesign of the total.

If, for instance the small signal part needs to be redesigned for a newer chipset, the rest can be the same. This is also true for the digital reception part, it can be modified without changing the other boards.

To support this flexibility a well defined interface is used in the form of a row connectors to interface the small signal board via the large signal board towards the digital reception part.

Another option is to change the large signal part from 50Hz to 100Hz application. Now the small signal board chipset is modified and a 100Hz converter box has to be added. This can be positioned in parallel behind the small signal board. In this situation the digital reception part needs no adaption. This 100Hz hybrid concept is not worked out.

The small signal board is positioned at the rear side of the cabinet. The peripheral connectors are also placed on the small signal part. This approach is not conventional. In current designs the peripheral connectors are mounted on the large signal board. In the presented design a lot of wiring, between the

small signal part, were the signal switching is done, and the large signal board, is not needed. This saves a lot of long wiring and board space.

Compared to our previous mid-end concepts GTV2000 or GTV3000, which were presented during IFA in 1997, the board space is now reduced with approx. 50%. This is also due to the fact that all used ICs are now SMD packages.

The ICs on the small signal board are located in such way that the minimum track length is needed from and to the peripheral connectors. For this reason the SCARTS are located between the digital sound IC and the TV processor.

The peripheral connectors are also used to make a separation between the mainly analogue processing part (like tuner, IF, TV processor) and the digital signal processing part (digital TV sound processor and TV controller) for better EMC behaviour.

The demo receiver is designed for the European market. For this reason SCART connectors are mounted, but on the same location, in a redesign cinch connectors can be placed.

The IF part is not full multi standard, only the european standards are supported. In case of DVB-T the "analogue" UV1316 tuner is replaced by the TD1544 COFDM tuner. The small signal board is prepared for that. Now also a mixer IC TDA9829T must be used to mix down the IF 36.15MHz to low-IF 4.57MHz for the VES9600. For DVB-T an extra position on the PCB is reserved for a second COFDM SAW filter.

In case of DVB-C a CD1516 tuner is used but than the extra SAW is not needed.

For EMC reasons the tuner is placed at the right hand side when you view the chassis from the rear side of the cabinet. Now we have the shortest ground connection from tuner ground towards the mains entry cord where

the Y capacitors are grounded. For injected current immunity this was seen as the most successful approach. The consequence is that the tuner is also very close to the horizontal deflection. To prevent magnetic coupling between the large signal part and the small signal part, the small signal board has a full copperplane at the rear side. This copper plane is not used as a jumper layer, all used jumpers are isolated wire jumpers on the component side (in production they can be replaced by  $0\Omega$  SFR16 jumpers).

To keep the price as low as possible, the board space of the small signal part must be kept small. For all ICs SMD packages are chosen. On the photo's the TV controller is mounted in a socket. This is only for the engineering phase. A metal mask programmed TV controller for production is soldered directly on the print.

First all SMD components are mounted, soldered by a reflow method. After that all leaded components and connectors are mounted which are flow soldered. In the presented setup the tuner must be mounted afterwards. We made not an industrial solution for this. Since conventional tuners have a straight connector outlet, they must be connected via a cable to an antenna entry mounted in the back cover of the cabinet.

If for EMC reasons the immunity for injected currents must be increased, this internal cable gives also the flexibility to apply a toroid inductor in this coax to avoid ground currents.

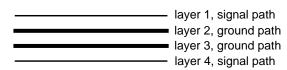

The digital reception board is positioned as far away as possible from the sensitive small signal IF part. To prevent magnetic coupling, the ICs on the digital reception part are mounted on the left side (seen from the overview photo position). The right side of this board is only a wire layer with some small SMD components. The two inner layers are full ground planes. This is different from the conventional 4 layer

# Application Note AN99061

setup were the inner layers are a ground plane combined with a power plane. The reason for this different approach is that with two inner ground planes the other two wire planes will have identical coupling to the inner layers. Another reason is that now with a relative small redesign effort a two layer version can be made. The two inner ground planes are taken out and the remaining wire layers are expanded with ground. Most likely the board space will increase a little but a two layer board is more cheap than four layers. This redesign is not done yet.

The large signal board is made with the new GreenChip SMPS controller. For low power stand-by mode an extra Greeny controller is reserved. The low voltage supplies for mainly the digital part are made with a small DC/DC convertor. The large signal board layout is made as compact as possible. Compared to our previous concept a 14% reduction on board space is achieved.

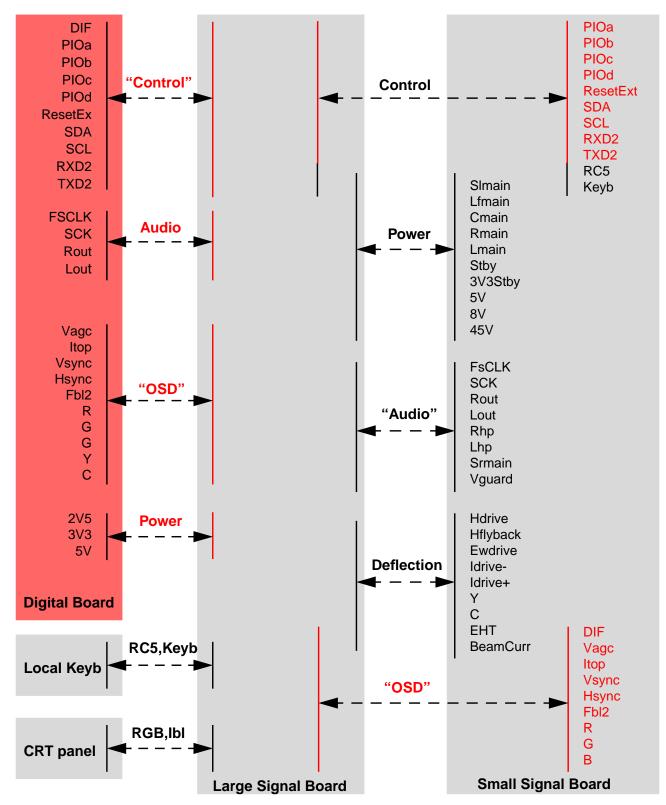

## 2.4 Analogue & Digital Interface

To support the separate functions (large signal - small signal - digital add-on, implemented as a three board setup) in an economically build receiver, a well defined (and stable) interface between the boards is needed.

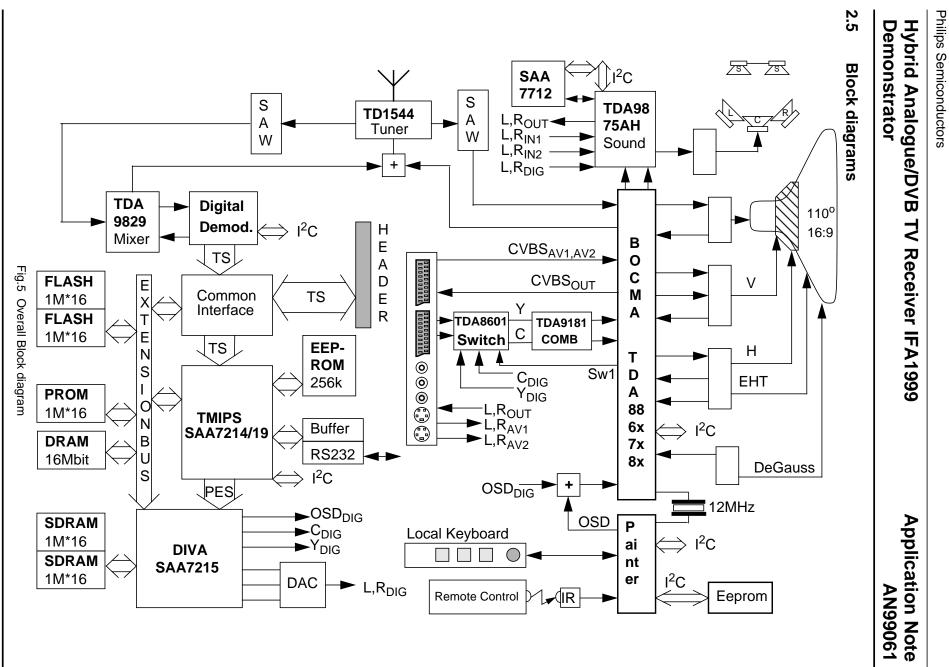

In the next two pictures the overall block diagram and the analogue to digital interface are drawn.

The pin sequence of the connectors on the interface board are chosen in such way, that on the small signal board the minimum amount of crossings are needed. On this, in fact single layer board, crossings of leads, are made with wire jumpers.

To further optimize the pin sequence, iterative checks were done for:

- the minimum crossings on the (single) layer large signal board

- a short connection between small signal and deflection part

- a short connection of tuner and IF circuitry

- a direct ground connection from tuner ground to mains entry safety capacitors (for EMC)

- short connection of audio and video in- and outputs towards the audio and video switching devices

- a separation of sensitive analogue and radiating digital circuitry

- the possibility for YUV interface expansion slot and the room for such an add-on board

- the same for an audio feature extension add-on board

- minimise the potential crosstalk between signals

These considerations eventual leaded to the presented location and orientation of the IC's and other components, in fact the layout of all three boards are related to the pin sequence in the interface connectors.

Another design goal was that the small and large signal interface connector can be used for both the hybrid and analogue only version. For this reason the signals which are needed for analogue are located in the centre of the connector row. The signals needed for hybrid are chosen at the begin and end of the connector row, for analogue only they can be omitted and a smaller connector can be used.

## Application Note AN99061

## 2.5.1 Analogue & Digital Interface Board

Philips Semiconductors

# Hybrid Analogue/DVB TV Receiver IFA1999 Demonstrator

Application Note AN99061

2.5.2 Analogue Reception Part

Fig.7 Analogue Reception Part: Block diagram

20

# Application Note AN99061

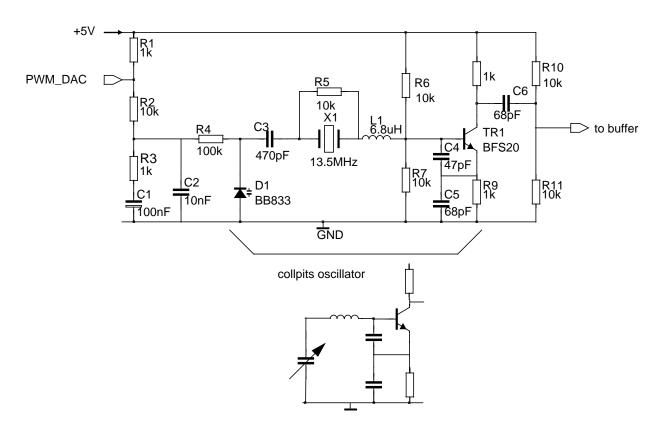

## 2.5.3 Digital Reception Part

Fig.8 Digital Reception Part: Block diagram

#### 2.5.4 Power Supply

Fig.9 Power Supply Part: Block diagram

### 3. Analogue Reception Part

The analogue reception part is a separate board containing ALL the small signal functions for a midrange TV receiver including tuner, peripheral connectors (two SCARTS, one input and one output SVHS connector), multistandard digital sound, comb filter and TV-controller. The core IC is an OneChip TV processor TDA8885 with development name BOCMA (Bimos One Chip for Mid-end Applications). This device covers all the processing from IF-in or external baseband inputs to RGB-out for a picture tube including the horizontal and vertical deflection control signals.

The tuner & IF part is designed in such way that different applications and/or TV receivers can be implemented on the same board. The different versions are made with different component settings and/or solder jumpers.

The target of this concept is that with one board design, two different types of receivers can be made:

- 1. Analogue Mid-Range TV set

- 2. Mixed digital/analogue hybrid TV set (indicated as LMR-DTV)

Via connectors extra functions can optional be added, like Dolby Pro Logic decoding and a simple PIP application. The sound add-on connector is prepared for a six channel audio decoding (like AC3) option. A YUV connector is present for additional picture improvements.

A lot of effort is put in the definition of an interface between the "analogue board", the "large signal board" and the "digital board". This interface is chosen in such way that future developments can be implemented (to a certain extend), like Scan Velocity Modulation, multi channel audio reproduction and direct digital interfacing of audio.

## 3.1 Tuner & IF Part

The concept is prepared for basically three types of tuners:

- 1. analogue tuners like UV1316

- 2. DVB-C tuners like CD1516

- 3. DVB-T tuners like TD1544

#### 3.1.1 Analogue only reception

For analogue reception an UV1316 can be used. This is a conventional three band PLL tuner with an IF frequency of 38.9MHz. The target of this reference design is to cover the European markets. For that reason the SAW filter application is not made full multi standard. The mid-end TV-processor TDA8885 has a quasi split sound with single reference IF-PLL demodulator. For the video SAW filter a type with double nyquist slopes was chosen; K3953M. For sound a switchable bandpass SAW filter is used; K9456M. This combination covers the standards B/G, I, D/K, L and L'. The sound bandpass filter is switched with the SW02 general output pin 60 of the TDA8885.

| TABLE 1  | SAW   | filter | switching |

|----------|-------|--------|-----------|

| SW02 (pi | n 60) | Sta    | ndard     |

| SWUZ (pin 60) | Standard       |  |  |  |  |  |

|---------------|----------------|--|--|--|--|--|

| 0             | L'             |  |  |  |  |  |

| 1             | B/G, I, D/K, L |  |  |  |  |  |

# Application Note AN99061

The BOCMA has an integrated group delay compensation. Now a multistandard SAW filter without group delay can be used and in case of B/G the internal B/G group delay is activated (bit GD).

With a different SAW filter choice other standards can be supported. An NTSC receiver can be made with e.g. an UV1336 tuner but than the SCART connectors need to be replaced by cinch connectors. The mounting of cinch connectors is not implemented in this board design.

## 3.1.2 Analogue and digital reception (DVB-C or DVB-T)

In case of an hybrid receiver the CD1516 or TD1544 is ALSO used for the analogue reception, there is NO need to use two tuners.

The application of a DVB-S front-end is not supported in this design. For a DVB-S hybrid receiver a different board setup with two tuners must be used (or a hybrid analogue terrestrial and satellite tuner must be developed).

In the IF part on the analogue board, the provision is made to have two different time constants for the tuner AGC. The time constant can separately be optimised for analogue and digital reception mode. Via a pushpull output port on the TDA8885 (pin 22, SW1) the analogue Aagc (SW1=0) or the digital Dagc (SW1=1) time constant is activated. The Philips 1300 (and 1500) tuner series must be alined to a maximum output level of  $105dB\mu V_{rms}$  which is equal to  $500mV_{pp}$  measured at an input level of 5mV or more via the tuner take over point settings in the BOCMA.

## 3.1.2.1 Hybrid IF part DVB-C

In the preparation phase of this hybrid reference design, the DVB-C QAM demodulator TDA8048 was on the IC roadmap. This product will now be replaced by the VES1820 and derivatives of it. For more information of TDA8048 see ref. [1]. The application of VES1820 or successors for this reference design are not implemented yet, it is just the replacement of TDA8048 by another device. The board setup and design will not change.

In case of DVB-C the Siemens/Matsushita SAW filter type X6966M is used. In that case the tuner IF frequency must be set to 36.15MHz.

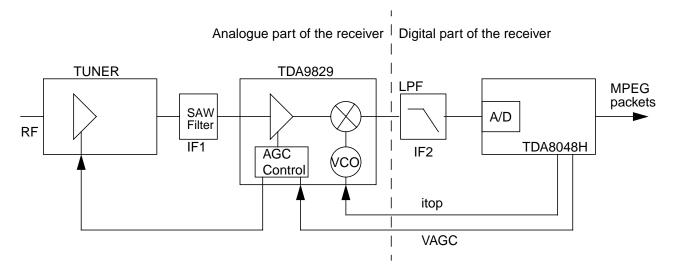

At the IF output of the tuner a down convertor TDA9829 is used to mix down IF to low-IF. After a lowpass filtering the ADC at the input of TDA8048 can convert the QAM carrier to the digital domain where it is further processed to a transport stream output format.

The TDA8048 controls the gain of the IF amplifier inside the TDA9829. The TDA9829 controls the tuner gain. The total gain is controlled by the TDA8048 in such way that the input voltage at the low-IF ADC TDA8048 input is constant. It is a closed loop feedback system. No adjustment is needed.

#### 3.1.2.2 Hybrid IF part DVB-T

The COFDM demodulator VES9600 IF application is basically the same as the DVB-C demodulator. Again a down convertor TDA9829 is used to make a low-IF signal which is fed to the VES9600. The successor VES9600/R will also support direct IF input at 36.15MHz, now the down conversion is not needed anymore.

#### 3.2 OneChip TV Part: TDA8885 (BOCMA)

The heart of the analogue part of the receiver is the TDA8885 which is a member of the TDA886X/7X/ 8X one chip TV processor family.

Common features of this IC family are:

- Multi-standard vision IF circuit with an alignment free PLL demodulator

- Internal time-constant for the IF-AGC circuit

- Integrated switchable sound trap and group delay correction for the demodulated CVBS signal

- Flexible source selection with CVBS switch and a Y(CVBS)/C input for comb filter

- Integrated chrominance trap circuit

- Integrated luminance delay

- Integrated chroma band-pass filter with switchable centre frequency

- Colour decoder which needs one 12 MHz reference crystal for all standards

- Blanking of the 'helper signal' for PAL<sup>PLUS</sup> and EDTV-2.

- Several picture improvements features

- Internal base-band delay line

- YUV interface

- Linear RGB input and fast blanking

- RGB control with CCC, white point and black level off-set adjustment

- Adjustable peak white limiting circuit

- Half-tone possibility

- Blue back option

- Horizontal synchronization with two control loops and alignment-free horizontal oscillator

- Vertical count-down circuit

- Vertical driver optimized for DC-coupled vertical output stages for improved geometry

- Low-power start-up for horizontal drive circuit

- IIC bus control of various functions

#### 3.2.1 BOCMA IF part

The BOCMA has an alignment free IF-PLL demodulator. The fully integrated oscillator is automatically calibrated, using the 12MHz crystal as a frequency reference. The IF frequency is simply set by I<sup>2</sup>C-bus bits **IFA**, **IFB** and **IFC**. All commonly used frequencies can be chosen. Depending on the SAW filter, 33.40 or 33.90MHz for SECAM-L1 in France, 38.00MHz for China, 38.90 for Europe, 45.75 for America and 58.75 MHz for Japan. The AFC information is available via I<sup>2</sup>C-bus bits **AFA**, **AFB**. Embedded software uses this for tuner frequency tracking (= "automatic following", AFC). The AFC window is typically 100kHz wide. This value is chosen higher than the 62.5 kHz tuning steps of a PLL tuner, to prevent the AFC loop from continuously adapting the tuning frequency. The internal AFC

accuracy is much less than 62.5kHz. For high speed search-tuning algorithms, the AFC window can be widened to approx. 300kHz via bit **AFW**=1.

Bit **STM** reduces the coincidence detector sensitivity (status bit **SL**). This bit can be used during search tuning to skip very weak signals.

Independent of video contents (detection is before video demodulation), the IF-PLL lock status can be read via bit **LOCK**.

The IF-PLL loopfilter is an external lead-lag RC filter. The described component values are optimised for the best demodulator performance in "normal" conditions. To partially cover non standard transmissions, e.g. excessive phase or frequency modulation of the picture carrier, via bit **FFI** the IF-PLL control speed can be increased. To further optimize the IF-PLL performance (e.g. to have the optimal step response for a 2T pulse for a certain SAW filter application, or have the minimum video to sound crosstalk), the DC-offset can be minimised via the **Offset** control bits. This extra alignment is only for those applications were this better quality is covered with a higher set price. For standard applications the center setting is recommended.

When switched to an external source, potential crosstalk of noise from the internal frontend (when tuner is not tuned), to the external signal can be reduced via bit **IFS**. This bit reduces the IF gain with 20dB.

The signal to noise ratio of the selected video can be read via bits **SN1, SN0**. This information can e.g. be used in a channel autostore, channels are stored in the order of S/N ratios.

Another status bit is **AGC**, it reflects whether the tuner gain control output is active or not. The point of tuner gain reduction can be set via **TOP** (tuner take over point) bits. The Philips 1300 (and 1500) tuner series must be alined to a maximum output level of  $105dB\mu V_{rms}$  which is equal to  $500mV_{pp}$  measured at an input level of 5mV or more.

The IF AGC time constant is in the BOCMA integrated and made switchable. With previous IC versions an external IF-AGC capacitor was used. The standard value was  $2\mu 2F$  which is now equivalent to the "norm" mode. The IF AGC speed can be adjusted with **AGC1**, **AGC0** bits.

| AGC1 | AGC0 | AGC speed  | Equiv cap. value | Function                                                                               |

|------|------|------------|------------------|----------------------------------------------------------------------------------------|

| 0    | 0    | 0.7 x norm | 3.1µF            | slow AGC, reserved for special field conditions                                        |

| 0    | 1    | norm       | 2.2µF            | normal recommended setting, optimal for both positive and negative modulation          |

| 1    | 0    | 2 x norm   | 1.1µF            | faster AGC for negative modulation as to<br>improve airplane flutter performance       |

| 1    | 1    | 4 x norm   | 0.5µF            | fastest AGC for negative modulation as to further improve airplane flutter performance |

#### TABLE 2 IF AGC speed settings

The BOCMA is available in FM-mono intercarrier and in QSS-SR versions. For this receiver the TDA8885 QSS with single reference is used. This IF concept has a better sound performance than intercarrier mode. For the French AM sound system the integrated AM demodulator of the BOCMA is used. On a separate pin the sound carriers are available. Baseband AM out and SIF output signals are routed to the TDA9875A sound device for further processing.

## 3.2.2 Colour decoding

The decoder frequencies of the various standards are obtained from an internal clock generator which is synchronized by an external 12 MHz crystal. Settings are made via IIC. 12MHz was chosen to match the reference frequency of conventional TV micro controllers. Now one crystal can be used for both TDA886x/7x/8x BOCMA as for SAA55xx/56xx Painter devices. Two types of applications are possible:

- 1. Painter has the crystal, being the clock master for the BOCMA slave.

- 2. Bocma has the crystal and Painter is slaved.

In both situations the master device xtal output pin is connected via a series capacitor of 33pF to the slave device xtal input pin. The slave xtal output pin is left open. Attention should be paid to the layout of this track. Keep this track as short as possible, avoid crosstalk from other surrounding tracks or elements! If these conditions can not be implemented, reconsider a two crystal application.

If the BOCMA is used as the clock master, the low-power start-up pin must be used and connected to a standby voltage supply between 3 and 5.5Volt (5mA current consumption). Now the BOCMA device has a continues operating clock oscillator which is needed for the micro controller.

In all cases the used BOCMA crystal must have a low frequency tolerance and stability for a proper colour catching range. A suitable crystal is the Philips/SaRoNix 9922 520 00169 in a conventional HC-49/U13 package ( $\Delta F_n$ =30ppm).

### 3.2.3 YUV interface

A YUV interface is placed at the PCB. An application with histo booster (TDA9171) or a PIP application with e.g. SAB908X can be made.

#### 3.2.4 Picture improvements

In the BOCMA various picture improvements features are integrated and can be controlled via IIC. In the embedded demo software for this receiver, most of the features can be controlled in the "Feature Menu". For production the setmaker can choose for no features, subsets or all features active to make a model range with the same chassis. Another option is to combine features to picture settings with names, e.g. "Bright", "Warm" etc. The features are shortly described in the next sub paragraphs.

#### 3.2.4.1 Video dependent coring

This is related to the peaking feature. The drawback of a peaking circuit is that noise in the video becomes more visible due to the peaking. Now the coring can be activated. Only in the low-light parts of the screen the noise is effectively reduced while still having maximum peaking in the bright parts of the picture. Three coring settings (and off) can be chosen with bits **COR1**, **COR0**.

#### 3.2.4.2 Colour transient improvement (CTI)

CTI decreases the rise and fall times of the colour difference signals. The colour transitions look more sharp. Bit **CTI** switches the function on and off.

#### 3.2.4.3 Dynamic skin control

Skin tones are very sensitive for hue errors, because we have an absolute feeling for skin tones. The goal is to make sure that skin tones are put at a correct colour. The dynamic skin tone correction circuit achieves this goal by instantaneously and locally changing the hue of those colours which are located in the area in the UV plane that matches skin tones. The correction is dependent on luminance, saturation and distance to the preferred axis and can be done towards two different angles. Depending on which part of the world there is a preferred skin tone. For example the 117 degrees angle can be the preferred skin tone in Asia where as in the USA and Europe the 123 degrees may be preferred. The preferred angle can be chosen via bit **DSA**, the correction range is 45 degrees. The function can be switched on and off with bit **DS**.

#### 3.2.4.4 Green enhancement

Green enhancement is intended to shift low saturated green colours towards more saturated green colours. This shift is achieved by instantaneously and locally changing those colours which are located in the area in the UV plane that matches low saturated green. Green enhancement is switched on and off via bit **GRE**.

#### 3.2.4.5 White stretch

White stretch adapts the transfer characteristic of the luminance amplifier in a non-linear way dependent on the picture content. It introduces additional overall gain for increased light production. For bright pictures the stretching is not active. Without increasing the brightness (black remains black) more details are visible in the darker parts of the picture. Via bits **WS1**, **WS0** three levels (and off) can be set.

#### 3.2.4.6 Black stretch

Black stretch corrects the black level for incoming video signals which have a deviation between the black level and the blanking level (back porch). This results in a maximum of visible details over the whole range of luminance. Bit **BKS** switches on and off.

#### 3.2.4.7 Blue stretch

Blue stretch is intended to shift colours near "white" with sufficient contrast values towards more blueish coloured white. A more sharp impression of the picture is percepted. The shift is accomplished by an offset at the RGB part of the BOCMA. Bit **BLS** switches on and off.

#### 3.2.5 RGB outputs & CRT board

The RGB outputs of the BOCMA are connected to the CRT board via three small series resistors. The cable from the small signal board to the CRT-board also contains the ground connection of the video amplifier.

The BOCMA contains a two point continuous cathode calibration circuit (CCC) which stabilises the black level (offset) as well as the cathode drive level (gain) of each gun of the CRT sequentially and independently on alternating fields. It is a timed DC controlled feedback loop.

On the RGB outputs at the start of every field reference pulses are generated. Via the video amplifiers this leads to a certain CRT cathode current which is fed back to the black current input of the BOCMA.

## Application Note AN99061

In one field a current reference of 8µA is used, in the next field a value of 20µA is used. From the result of these pulses information of the CRT black level AND the amount of gain in the RGB path is generated. The black level of the BOCMA RGB outputs is adapted to the CRT black level and via the **CL** bits the drive level is set. Note that with this two point loop the video amplifier gain has NO effect on the CRT drive level anymore!

The black current feed-back line is the most sensitive part of the loop. For this reason some precautions have to be taken to avoid instability. If a flatcable is used (most of the cases) avoid crosstalk and separate the RGB wires (CCC-loop output) with the ground wire from the black current info wire (CCC-loop input). The preferred order is: BLKIN, GND, R, G, B.

A second precaution is to apply some filtering on the black current feed-back signal. In the design a capacitor (330pF) to ground (ground this capacitor to the "guard ground ring" if applicable), connected to the black current feed-back line coming from the CRT is used. From this point a series resistor ( $10k\Omega$ ) routes CCC info to the pin 30 of the TDA8885H. In this way all the black level info return current from theTDA6108 is first integrated (=low-pass filtered) and partial converted to a voltage by the capacitor. The series resistor converts the voltage back to current info.

On the CRT board a TDA6108 triple video amplifier with black current output is used. This device has a fixed gain of 51. To reduce the gain to approximately 45, three series resistors have been added directly at the RGB inputs of the TDA6108 (to prevent additional low-pass filtering due to the series resistor and the parasitic capacitance of a long RGB to CRT cable).

The gain of 45 is needed to obtain a more robust operating black current loop for a large variety of picture tubes. For the same drive level (which is measured via the black current loop and therefore can be controlled in the BOCMA via the **CL** bits) and a reduced video amplifier gain, the video input voltage is increased. In this way a better signal to disturbance ratio for the RGB signals is obtained.

The outputs of the video amplifiers are connected to the picture tube via special flash-proof resistors. All tube electrodes, not connected to ground, contain a spark-gap connected to the aqua-dag ground. The focus spark-gap is integrated in the tube socket connector. The aqua-dag ground is connected to the ground of the line transformer. This configuration has been selected to keep flash-over-currents in a loop as small as possible.

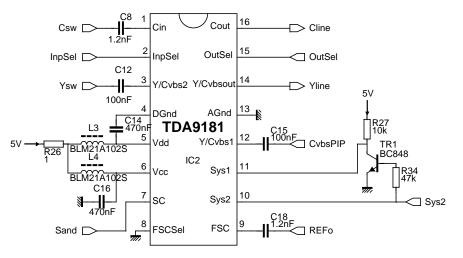

#### 3.3 Comb filter

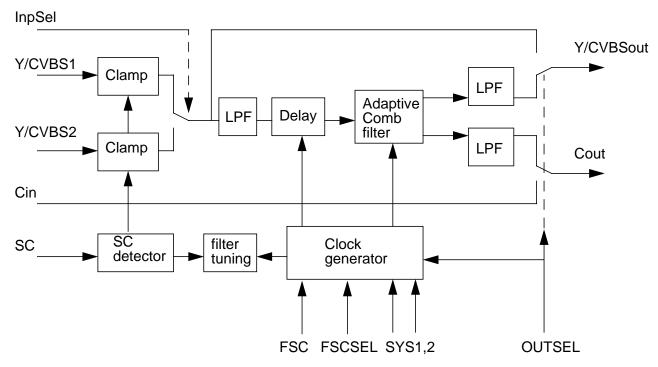

The TDA9181 is a multistandard PAL, PAL-M, PAL-N and NTSC comb filter IC with internal delay lines, filter, clock control, synchronization and signal switching. The application diagram is given below.

Fig.9 Comb filter application diagram

# Application Note AN99061

The Y/CVBS inputs are clamped by means of an internally generated clamp pulse which is derived from the sandcastle input (Sand).

The input switch (InpSel) determines which input signal passes through a low pass filter.

A colour subcarrier frequency signal (REFo) from the BOCMA is coupled via an external capacitor to the TDA9181.

The supply lines are filtered with series coils, a good ground plane under the IC is important as well as short decoupling.

The system switches (Sys1 and Sys2) determine which colour standard is used. For this Europe only receiver just two colour standards are implemented (PAL and NTSC) with one sys line (Sys2) which is controlled by the TV micro controller (Painter). If PAL-M and PAL-N has to be supported a second sys line is needed. The comb filter system truth table is given below.

#### TABLE 3 Comb filter colour standards

| SYS1 | SYS2 | <b>Colour Standard</b> |

|------|------|------------------------|

| 0    | 0    | PAL-M                  |

| 0    | 1    | PAL                    |

| 1    | 0    | NTSC-M                 |

| 1    | 1    | PAL-N                  |

The internal comb filter block diagram is given below.

Fig.10 Internal comb filter block diagram

The output switch (OutSel) is not used in this application, the pin must be left open, now the pin is pulled-low by the comb filter (comb filter on condition). Note that the pull-up resistor at the Painter side is removed! The FSC (f subcarrier) is the REF output from the BOCMA, this signal is a sinewave with

# Application Note AN99061

the actual subcarrier frequency. FSCSEL is not used and forced low (REF=1 x  $f_{sc}$ ). If FSCSEL is high you can apply a 2 x  $f_{sc}$  frequency signal to FSC. When there is no REF signal coming from the BOCMA, or the comb filter can not lock to it, the comb filter switches itself in the bypass mode. In the BOCMA the REF output can be switched off via IIC (bits **CMB0, CMB1**). In this way the comb filter is switched on and off.

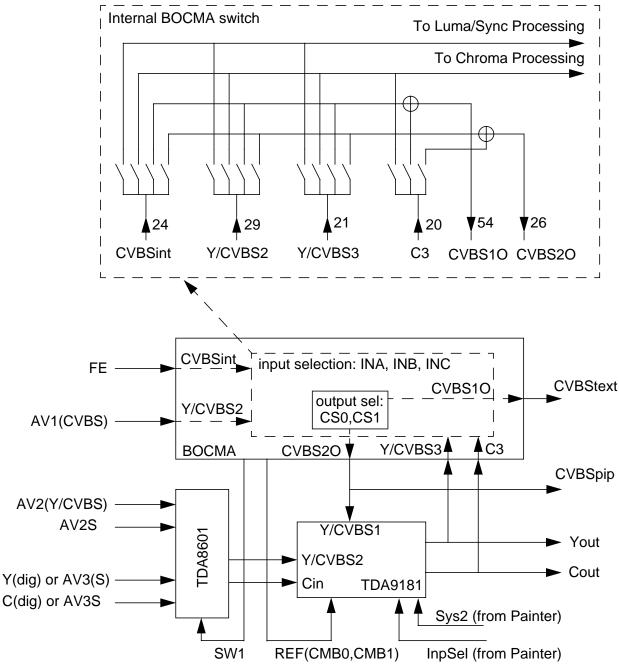

## 3.4 Peri & Switching

Without the digital add-on, source switching is possible between front-end, AV1(CVBS or RGB), AV2(CVBS or Y/C), AV2-S, AV3 and AV3S (note: AV2S and AV3S is not supported by the current software). Source switching is done directly with IIC in the BOCMA or indirectly via a BOCMA output pin SW1 which controls an external switching IC (TDA8601). For SVHS recording a Y/C output is made available (Yout, Cout).

## Application Note AN99061

When the digital add-on is used, AV3(S) is sacrificed and now used as the input for the digital reception part. The next diagram shows the peri switching.

In the internal BOCMA switch CVBS1O is identical to the selected signal that is applied to the internal video processing, so coupled to the displayed source. This output can be used for teletext aquisition and is therefore routed to the Painter. CVBS1O can also be used to make a video monitor output which is needed for the Asian market.

CVBS2O can indepently be switched to any input with bits CS0,CS1. This output is used for PIP or a

## Application Note AN99061

comb filter. The PIP application in combination with a comb filter can be made with an extra source switching IC for PIP. The comb filter only application is implemented.

The next table shows all the bit and pin settings for the peri switching.

| <b>INA</b><br>0<br>1 | <b>INB</b><br>0       | <b>INC</b>                      |                                           | CS0                                                                                                                                                                                                                                                                                                                                         | SW1                                                                                                                                                                                                                                                                                                                                                                               | CMB1                                                 | CMB0                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | InpSel                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|----------------------|-----------------------|---------------------------------|-------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| č                    | 0                     | 0                               | ~                                         |                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                   |                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | inpoer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 1                    |                       | 5                               | 0                                         | 0                                                                                                                                                                                                                                                                                                                                           | 0                                                                                                                                                                                                                                                                                                                                                                                 | 1                                                    | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                      | 1                     | 1                               | 0                                         | 0                                                                                                                                                                                                                                                                                                                                           | 0                                                                                                                                                                                                                                                                                                                                                                                 | 0                                                    | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 0                    | 0                     | 1                               | 0                                         | 1                                                                                                                                                                                                                                                                                                                                           | 0                                                                                                                                                                                                                                                                                                                                                                                 | 1                                                    | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 1                    | 1                     | 1                               | 0                                         | 1                                                                                                                                                                                                                                                                                                                                           | 0                                                                                                                                                                                                                                                                                                                                                                                 | 0                                                    | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 0                    | 1                     | 1                               | 0                                         | 0                                                                                                                                                                                                                                                                                                                                           | 0                                                                                                                                                                                                                                                                                                                                                                                 | 1                                                    | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |